Isi

- Definisi - Apa yang dimaksud dengan Staggered Pin Grid Array (SPGA)?

- Pengantar Microsoft Azure dan Microsoft Cloud | Sepanjang panduan ini, Anda akan mempelajari tentang apa itu cloud computing dan bagaimana Microsoft Azure dapat membantu Anda untuk bermigrasi dan menjalankan bisnis Anda dari cloud.

- Techopedia menjelaskan Staggered Pin Grid Array (SPGA)

Definisi - Apa yang dimaksud dengan Staggered Pin Grid Array (SPGA)?

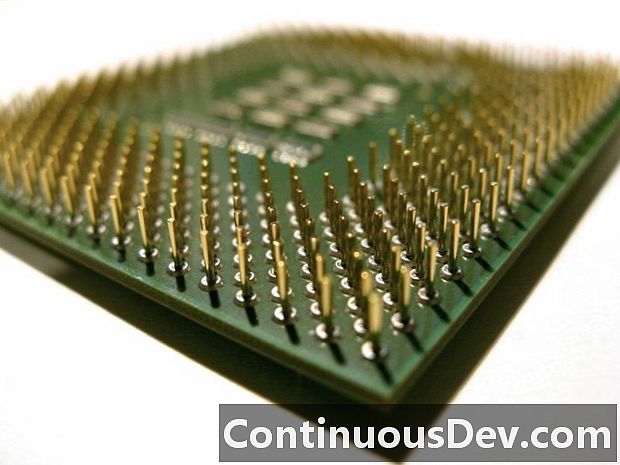

Pin grid array (SPGA) yang terhuyung-huyung adalah gaya soket sirkuit terpadu atau pin-out yang memiliki jaringan pin yang terhuyung-huyung yang mengelilingi tepi soket, ditempatkan sebagai beberapa kotak, satu di antara yang lain. Struktur ini juga dikenal sebagai kotak berpotongan.SPGA umumnya digunakan pada motherboard untuk prosesor berbasis pada platform Socket 5, Socket 7 dan Socket 8.

Pengantar Microsoft Azure dan Microsoft Cloud | Sepanjang panduan ini, Anda akan mempelajari tentang apa itu cloud computing dan bagaimana Microsoft Azure dapat membantu Anda untuk bermigrasi dan menjalankan bisnis Anda dari cloud.

Techopedia menjelaskan Staggered Pin Grid Array (SPGA)

Dalam array pin grid terhuyung-huyung (SPGA), pin disusun dalam baris diagonal. SPGA mencakup dua susunan pin persegi, seimbang di kedua arah. Dengan kata lain, pin disusun untuk membentuk kisi kuadrat diagonal di dalam batas kuadrat. SPGA mencakup area di tengah paket di mana tidak ada pin yang diatur. Paket SPGA ideal untuk perangkat yang menuntut kepadatan pin lebih tinggi dibandingkan dengan apa yang ditawarkan oleh array pin grid (PGA).Sirkuit terpadu awal memiliki pin yang disusun menggunakan PGA, yang mengatur pin dalam struktur seperti grid. Kemajuan dalam desain prosesor dan permintaan untuk pin lebih banyak membuat PGA tidak sesuai dan ketinggalan zaman. Tujuan utama SPGA adalah untuk mengurangi ukuran mikroprosesor ketika pin lebih banyak diperlukan. Struktur SPGA digunakan oleh prosesor yang berpusat pada teknologi Socket 5, Socket 7 dan Socket 8.

Keuntungan menggunakan formasi SPGA yang bertentangan dengan versi sebelumnya adalah bahwa ia terdiri dari pin yang lebih dekat, sehingga memungkinkan lebih banyak pin untuk area permukaan tertentu. Hal ini memungkinkan untuk penurunan ukuran microchip atau, dengan kata lain, menawarkan kapasitas transfer yang lebih baik dalam chip berukuran serupa.